AMD Unveils Zen 2 EPYC 7nm CPU With 2X Performance Per Socket, Zen 3 Set For 2020 - Updated: Benchmarks

AMD CEO Dr. Lisa Su says that the company is "betting big on 7nm" and the innovations that come with it. AMD claims Rome will be the world's first 7nm datacenter CPU, will offer increased instructions per clock (IPC) thoughput and a big overall performance uplift.

The road to Zen began back in 2012 when AMD first started designing Zen architecture. Zen started at 14nm, while Zen+ brought it down to 12nm with further optimizations. However, AMD felt that going down to 10nm wouldn't allow for a big enough performance boost for its customers, so the company pushed down a full process node to 7nm, which AMD thinks will have a long life in its product life-cycle (hopefully not as long as Intel's 14nm node and the company's missteps to 10nm). Regardless, this process migration has allowed AMD to double chip density by 2X, halve power consumption, and deliver claimed boost in overall IPC performance by 25 percent compared to its previous gen Zen+ architecture.

The move to 7nm also allowed AMD to make the following advances with its Rome-based EPYC processor core microarchitecture:

- 2X Performance per Socket

- 4X Floating Point performance per socket

- Previous gen socket compatible

- Forward compatible with next gen Milan platform that supports PCI Express 4 connectivity

- Improved branch prediction

- Better instructions prefetch

- Re-optimized micro-op instruction cache

- Increased the size of the micro-op cache

- Doubled floating point width to 256-bit

- Doubled load store bandwidth

- Increased dispatch and retire bandwidth

- Results in maintained high throughput for all modes

Update: 11/6/18 - 2:26PM - We are continuing to update features and specification information on AMD's 2nd Gen EPYC Zen 2-based processors as they come in from the Next Horizon event. In a separate break-out session, AMD CEO Dr. Lisa Su noted that the company's 7nm Second Gen EPYC Rome processor top-end CPU will be 64-core, 128-thread beasts that are socket-compatible to the previous gen EPYC platforms as well as the company's next-gen Milan server platform that supports PCIe 4. As a result, 7nm Rome 2nd Gen EYPC server processors will offer 2X overall performance per socket and 4X the floating point performance.

AMD execs then teed up a demo of a dual-socket Intel Xeon Platinum 8180M server (56 cores total, 28 per socket, 112 threads), competing against a single-socket AMD Rome EPYC 64-core server running C-Ray, a raytracing benchmark designed to showcase floating-point CPU performance. The AMD EPYC Rome server was running air-cooled, at stock frequency and was in a prototype system that AMD has yet to optimize fully. As you might expect, the single socket, 64-core EPYC server edged-out Intel's Platinum-class dual socket server with ease. Take a look...

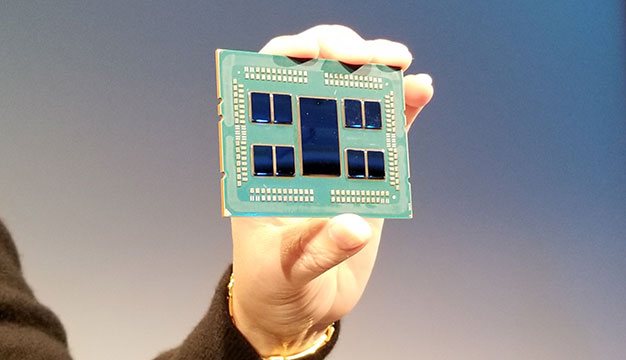

In addition, AMD has been able to add some security enhancements with Zen 2 as well, including hardware mitigation for recently discovered Spectre CPU vulnerabilities. AMD has also increased the number of encryption keys for virtualization to allow companies to support more virtual machines. Infinity Fabric is now in its second generation, and I/O per die has been optimized to improve both latency and power. Finally, while Infinity Fabric and the IO controller complex itself is being kept on a 14nm process, the accompanying chiplets for Zen 2 CPUs will be built on 7nm process technology. Those Zen 2 CPU complexes have Infinity Fabric interfaces on them and then connect to the IO controller and Infinity Fabric chip, which is on a single 14nm die (see the beastly representation of this in Dr. Su's hand above). AMD execs also noted that significant advancements have been made with infinity fabric and the memory latency story between CCXs (CPU Complexes) "is a good one."

AMD's latest EPYC processors will be facing some stiff competition in the form of Intel's Cascade Lake-SP and Cascade Lake-AP processors. Both are based on Intel's 14nm++ manufacturing process, but the former is expected to ship before year's end. The latter will ship in the first half of 2019 and will be available in two-socket configurations. Cascade Lake-AP processors will be available with up to 48 cores, which means that dual-socket systems will have a total of 96 physical cores on-board and the potential for 192 total threads.