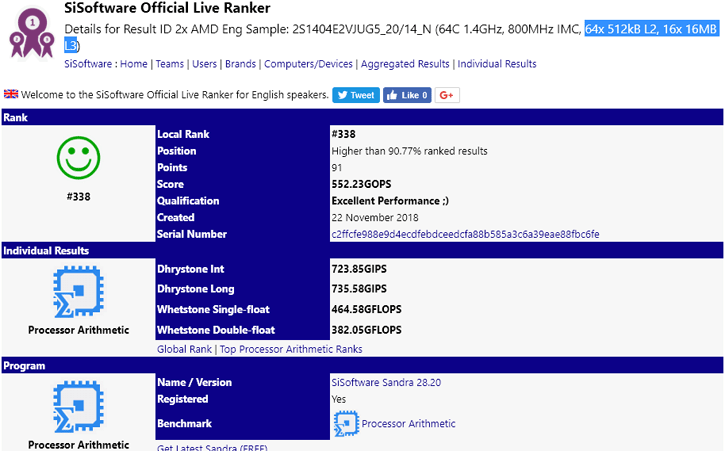

We've been going back and forth on AMD's 7nm ZEN. We've seen the announcements and the hype is real for 2019 when the first products will be released. The first series, of course, will be for Epyc, the server products, with up to 64-cores I might add. In the SiSoft Sandra Database, a first entry has been found and is showing interesting stuff.

The part listed is ROME (actually it is a server with two of these puppies (that's 128 cores / 256 threads)) and was spotted and posted at reddit. Anyway, ROme is the 64-core part. Here's the interesting part, the database entry shows a setup based on 512 KB dedicated L2 cache per core, and then 16x 16 MB L3. So each CPU block is tied to 16 MB L3. Sixteen L3 partitions indicate 4 cores per chiplet (4x16=64 cores). For example, the Ryzen 7 2700X the L3 cache is arranged as "2x 8 MB L3," here each CCX holding four cores has an L3 cache amount of 8 MB. All things considered, we cannot 100% trust a SiSoft Sandra early listing though. But if true, it's pretty huge progression.

These processors are of course data-center products, but you know it, this architecture always end up in desktop processors. A number of announcements have been made, yes Zen2 is based on 7nm, yes AMD has working samples and yes they will arrive in 2019. So far all it pretty interesting. AMD expects a 25% generational performance increase for the CPU cores. While that's not IPC, the theory is that one die package would be 25% faster.

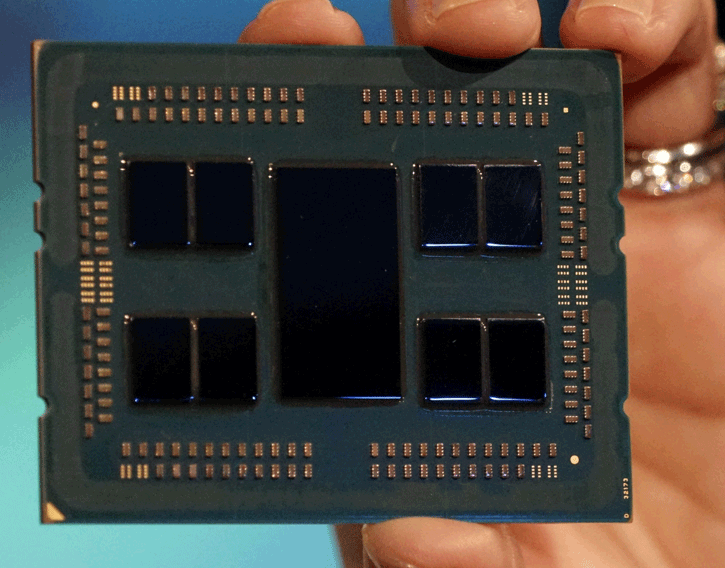

ZEN2 is not just a die-shink, it's new architecture and the rumor from a while ago was true, it's based on chipsets. 7nm dies surrounding one 14nm IO chip in the center connected through AMD's Infinity fabric. The "Zen 2" high-performance x86 CPU processor core thus has a modular design methodology. An improved AMD Infinity Fabric interconnect links the separated pieces of silicon ("chiplets") within a single processor package. So that is why you see nine dies.

This should solve some latency issues. The new processor also will support 8-channel DDR4 memory. Also, PCI-Express will be supported. Rome looks amazing, the dies are just so small.

AMD ZEN2 Rome Listed in Sandra, shows doubled up L3 caches