SAN FRANCISCO—Intel today gave the first peek at what makes its new Skylake processors tick. The company is still being peculiarly coy about the new processors—many details won't be revealed until the company announces its Xeon server processors—but shared some details of the processor's architecture and described its many and varied tricks to cut power usage.

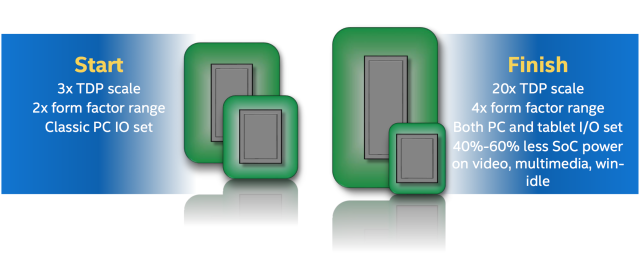

As has been the case for many years now, reducing power consumption remains Intel's top priority for Skylake. Not only does reduced power consumption enable the company's processors to be used more widely—client Skylake processors will span everything from 4.5W tablet and ultralight systems up to 95W desktop devices, a 20-fold difference in power envelope—it also enables greater performance. Reduce the power used by one part of the chip and the extra thermal headroom (and current draw) can be spent on other parts of the chip; this is the underlying principle of Turbo Boost.

Intel's focus on Skylake's power-saving capabilities isn't too much of a surprise, given this overriding concern. But it's not the sole concern. The greater power flexibility has in turn created other demands. For example, the package size and motherboard size matter: it's no good having a 4.5W processor for laptops and tablets if the package is huge. The difference between the smallest and largest packages in Skylake isn't as pronounced as the power difference—only a four-fold difference—but it's still significant. Skylake's mobile and SoC processor packages are smaller than those of comparable Broadwell packages, enabling smaller, lighter systems. Its motherboards should be smaller, too, thanks to power supply optimizations.

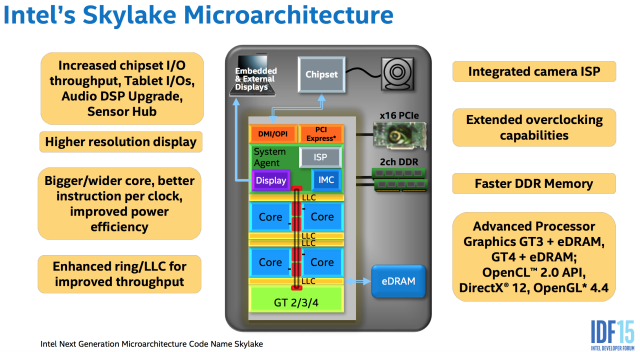

These low-power use cases have also prompted inclusion of low-power, tablet-oriented I/O systems, too. Tablets and smartphones typically use eMMC for storage, SDXC for expandable storage, and CSI for integrated cameras; as such, at least some of Skylake's chipsets also include these buses.

Also with an eye on this market, some Skylake chipsets will include image signal processors similar to those found in smartphone processors. These ISPs will support up to four 13MP cameras (with two active simultaneously) and include hardware support for a range of image processing tasks: video capture (1080p60 and 2Kp30), face detection including smile/blink detection, burst capture, panorama capture, and HDR capture.

What we know of the architecture

All this isn't to say that performance doesn't matter at all, of course. Intel did describe some of the performance changes it has made in Skylake, so while details are limited, we'll start there. For the most part, Skylake brings a series of incremental improvements, making it a little wider—able to dispatch more instructions at once—and a little better at extracting parallelism. It can fetch and dispatch, in some circumstances, up to six instructions at once, with up to 224 instructions in its out-of-order buffer at once (up from 192 in Haswell).

Prefetching has been made smarter, including optimizations to reduce prefetching when the processor detects that it's not helpful, such as if excessive speculative execution is occurring. This in turn saves power budget, giving more freedom to use that power elsewhere, such as for hitting higher frequencies.

Some instructions have been made faster, with Intel claiming that the AES acceleration instructions have increased encryption performance by up to 33 percent (in CBC mode) or 17 percent (in GCM mode).

The ring buffer that Intel uses to connect all the cores in a processor to the GPU, memory controller, and I/O blocks has also been made faster. The company says that its throughput has doubled, enabling higher performance at the same power cost. Alternatively, Skylake can offer the same level of throughput at a reduced power cost, depending on what the current situation requires. The support for DDR4 should increase memory bandwidth.

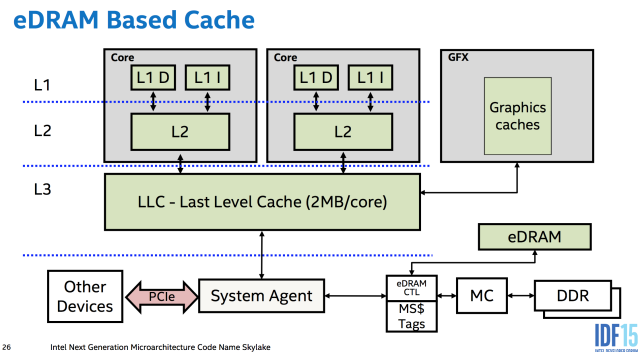

The eDRAM cache that Intel supported on a handful of Broadwell systems has also been revamped. In Broadwell, each core pair had 1.5MB of level 3 cache, and the eDRAM, when it was included, was a 128MB level 4 cache that held data evicted from the level 3 cache. In Skylake, the level 3 has been bumped up to 2MB per core pair, and the level 4 cache is gone.

Instead of being a level 4 cache, the eDRAM is now what Intel calls a memory side cache. In Broadwell, the eDRAM was notionally connected to level 3, to store data that the level 3 cache no longer had room for. In Skylake, the eDRAM is now connected between the integrated memory controller and the "system agent;" the portion of the processor that handles, among other things, cache coherence (ensuring that different cores see a consistent view of shared data).

With this new design, the eDRAM is always coherent, since it is privy to all writes made to main memory, regardless of which core makes them. This also means that it can cache any data, even if it's stored in memory that is marked as "uncacheable" by the operating system. The design also enables both PCIe devices and the display engine to read to and write from the cache.

Intel's representatives were strangely reluctant to describe what all these changes meant in real terms. When asked what kind of instruction-per-cycle improvement they yielded over Broadwell, they offered no answer, suggesting instead that people look at the public benchmarks already available for the i7 6700K. This was a strange response, because Intel must surely have some idea of what performance gain these modifications achieve, and there seems little harm in disclosing it. Isolating individual improvements in general system benchmarks of the kinds used to test the i7 6700K is difficult, and one came away with the impression that perhaps the company was trying to hide something. We've heard that gains of around 10 percent are expected—we just wish Intel would say something officially.

Making Skylake more miserly

But power is the biggest consideration. Skylake has some "more of the same" aspects to its power conservation—more individual parts of the processor can have their frequency adjusted or powered down to allow finer tuning of power consumption—though these have been extended. For example, most code either never uses the AVX2 instruction set, or uses it extensively; it's rare for applications to only use AVX2 every now and then. When faced with workloads that never use AVX2, those instruction units are powered down.

The most significant power saving feature is called Speed Shift Technology. Currently, power management is a task that's split between the processor itself and the operating system. When the processor is operating at its highest guaranteed frequency (the "base" frequency used on spec sheets and product boxes), called P1, turbo boosting (temporarily increasing the frequency when not all cores are in use, a state called P0) is enabled and performed by the processor's own power management hardware. When operating at frequencies below P1 (called P2, P3, etc.), the power management is done by the operating system. The system's firmware offers the operating system a range of different frequencies to choose from, and the operating system picks one depending on the current workload, power priorities (maximum performance versus maximum battery life), and temperature.

In Skylake, the power management is more cooperative. The operating system still has some control—for example, it can force a low frequency for extending battery life, or more commonly, it can set a range of acceptable frequencies—but the processor itself handles the rest. Rather than just choosing between P0 turbo states, the processor can pick between the full range of P states, from the minimum frequency all the way up to P0.

This makes power management far more responsive. The old way was relatively slow; it takes about 30 milliseconds for the processor to inform the operating system that something has happened (the workload has gone up, the system is getting too hot, etc.) and for the operating system to then respond (increase the frequency to handle the workload, reduce the frequency to reduce power draw). In the new system, that time is cut to about 1 millisecond. This means that the processor is both quicker to react to new work, boosting the frequency as needed, but also much quicker to cut the frequency when idle. Skylake processors will pick the most efficient frequency to run at, without needing operating system oversight. They'll also be able to go as slow as 100MHz if that's all that's needed.

Skylake systems-on-chips will offer another power saving feature: duty cycling. The processor's energy consumption is proportional to the square of the frequency, which is why cutting the frequency is so important to saving energy and increasing the battery life. But at low frequencies, the frequency-dependent energy consumption is no longer the dominating factor. Instead, things such as leakage (the small currents that flow though transistors even when they're "off") dominates. Once this threshold is reached, reducing the frequency further to save energy doesn't work. In fact, it makes energy usage worse: a lower frequency means that calculations take longer, meaning it takes longer for the processor to switch to its lowest "off" state.

So what Skylake will do is duty cycle: instead of switching to ever lower frequencies, once it reaches the most efficient frequency it will cut energy usage further by cycling between this efficient frequency and suspended in the C6 power state.

The Skylake GPU also gets in on the power-saving act. We have a detailed look at what's new for Skylake's graphics, but important for power saving is the new dedicated video codec hardware. This means that common use-cases, such as watching a movie or video conferencing, can be done in highly efficient fixed-function circuits, rather than using the more flexible, but more power-hungry, CPU or GPU cores. As a result, Skylake should last even longer on battery when watching movies, especially if Intel uses the new H.265/HEVC codec.

While Intel is still keeping us waiting when it comes to a full look at Skylake's internals, the incremental improvements to the architecture and new power management features mean that it's set to continue the pattern of the last decade or so: a little bit faster, and a little bit less power-hungry, making Intel processors suitable for an ever-increasing range of devices.

Listing image by Intel

reader comments

111